# HI2570, CXD2570

NOT RECOMMENDED FOR NEW DESIGNS

# 1-Bit AD/DA **Converter For Audio Application**

September 1997

#### Features

- Two-Channel AD/DA Converters and Their Each Decimation and Oversampling Digital Filter in a Single Chip

- · Simplified External Parts with a Built-In Analog Circuit Around AD Converter

- Distortion

- ADC ..... 0.015%

- DAC ...... 0.009% (-3dB) • S/N Ratio (Typical Values when F<sub>S</sub> = 16kHz)

- Ripple in the Digital Filter Pass Band ......±0.05dB<

- Attenuation in the Digital Filter Rejection Band... 45dB>

#### Applications

- Telephones, TV Conference Systems, Language Laboratory Equipment, TV Game Equipment and Electronic Musical Instrument

## Ordering Information

| PART<br>NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE    | PKG. NO.    |

|----------------|----------------------------------|------------|-------------|

| HI2570JCQ      | -20 to 55                        | 48 Ld MPQF | Q48.12x12-S |

| CXD2570Q       | -20 to 55                        | 48 Ld MPQF | Q48.12x12-S |

# Description

The HI2570, CXD2570 is a 1-bit stereo AD/DA converter which uses a 2nd-order  $\Delta \Sigma$  system noise shaper. This LSI is especially suited for sampling frequency between 8kHz and 32kHz.

### Function

- Data Can Be Input/Output at Rate of 1xF<sub>S</sub> with a Built-In Digital Filter

- Multi-Channel Systems can be Connected Using Several HI2570, CXD2570Qs

- The 32-Slot Serial Data Interface Enables Independent Selection of Data Frontward Truncation/Rearward **Truncation and MSB First/LSB First**

- $512F_S/1024F_S$  (when  $F_S = 8$  to 16kHz) or  $256F_S/512F_S/$  $768F_S/1024F_S$  (When  $F_S$  = 16 to 32kHz) Can be Used as the Master Clock

- The Sampling Frequency of Not Only 8kHz or 16kHz, but 32kHz or 44.1kHz Can Be Used for Audio Equipment

- Various Frequency Divided Clocks are Output for LSIs Connected

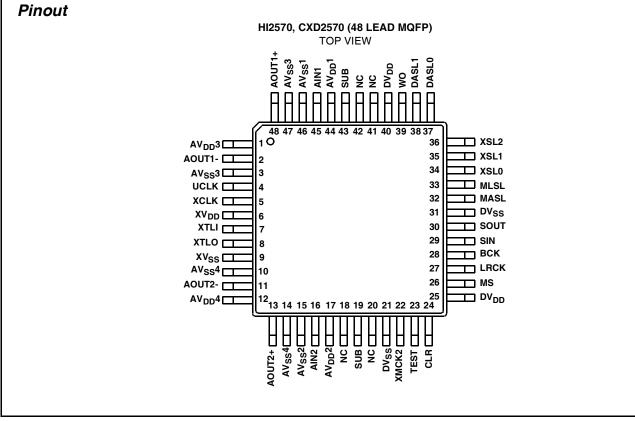

# **Pin Descriptions**

| PIN NO. | SYMBOL             | I/O | DESCRIPTION                                                                                                                                                                                             |  |  |  |

|---------|--------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | AV <sub>DD</sub> 3 | _   | Analog power supply for channel-1 DA converter                                                                                                                                                          |  |  |  |

| 2       | AOUT1 (-)          | 0   | Analog reversed phase output of channel-1 DA converter                                                                                                                                                  |  |  |  |

| 3       | AV <sub>SS</sub> 3 |     | Analog GND for channel-1 DA converter                                                                                                                                                                   |  |  |  |

| 4       | UCLK               | 0   | Outputs a 1/2 frequency divider of clock input from oscillation pin XTLI (Pin 7)<br>User clock output for the externally connected ICs.                                                                 |  |  |  |

| 5       | XCLK               | 0   | 256Fs/512Fs clock output. This provides the master clock for ICs operating in the slave mode when multiple CXD2570Qs are connected.                                                                     |  |  |  |

| 6       | XV <sub>DD</sub>   | _   | Digital power supply for the master clock                                                                                                                                                               |  |  |  |

| 7       | XTLI               | I   | Crystal oscillation circuit input. Connects the crystal oscillator selected by the crystal selector pins XSL0 to 2 (Pins 34, 35 and 36). To input an external mas ter clock, this pin is used.          |  |  |  |

| 8       | XTLO               | 0   | Crystal oscillation circuit output. Connects the crystal oscillator selected crystal selector pins XSL0 to 2 (Pins 34, 35 and 36).                                                                      |  |  |  |

| 9       | XV <sub>SS</sub>   | —   | Digital GND for the master clock                                                                                                                                                                        |  |  |  |

| 10      | AV <sub>SS</sub> 4 | _   | Analog GND for channel-2 DA converter                                                                                                                                                                   |  |  |  |

| 11      | AOUT2 (-)          | 0   | Analog reversed phase output of channel-2 DA converter                                                                                                                                                  |  |  |  |

| 12      | AV <sub>DD</sub> 4 |     | Analog power supply for channel-2 DA converter                                                                                                                                                          |  |  |  |

| 13      | AOUT2 (+)          | 0   | Analog forward phase output of channel-2 DA converter                                                                                                                                                   |  |  |  |

| 14      | AV <sub>SS</sub> 4 | _   | Analog GND for channel-2 DA converter                                                                                                                                                                   |  |  |  |

| 15      | AV <sub>SS</sub> 2 | _   | Analog GND for channel-2 AD converter                                                                                                                                                                   |  |  |  |

| 16      | AIN1               | I   | Analog input of channel-2 converter                                                                                                                                                                     |  |  |  |

| 17      | AV <sub>DD</sub> 2 | _   | Analog power supply for channel-2 AD converter                                                                                                                                                          |  |  |  |

| 18      | NC                 | _   |                                                                                                                                                                                                         |  |  |  |

| 19      | SUB                | -   | Connected to the substrate in the IC (having the same potential as power sup<br>ply). Connect this pin to GND via a capacitor on the external printed wiring<br>board.                                  |  |  |  |

| 20      | NC                 | _   |                                                                                                                                                                                                         |  |  |  |

| 21      | DV <sub>SS</sub>   | _   | Digital GND                                                                                                                                                                                             |  |  |  |

| 22      | XMCK2              | 0   | IC measurement. Normally, Low is output.                                                                                                                                                                |  |  |  |

| 23      | TEST               | I   | Test. Normally, fixed at Low. Equipped with a pull-down resistor.                                                                                                                                       |  |  |  |

| 24      | CLR                | I   | System clear input. Normally, fixed at High; cleared at Low. Equipped with a pull-up resistor.                                                                                                          |  |  |  |

| 25      | DV <sub>DD</sub>   | —   | Digital power supply.                                                                                                                                                                                   |  |  |  |

| 26      | MS                 | I   | Master/slave mode switching input. High = Master mode. Low = Slave mode Equipped with a pull-up resistor.                                                                                               |  |  |  |

| 27      | LRCK               | I/O | Sampling frequency clock pin of serial I/O. Outputs in master mode (when Pir 26 is High). Inputs in slave mode (when Pin 26 is Low). Transfers channel-1 data at High; transfers channel-2 data at Low. |  |  |  |

# HI2570, CXD2570

# Pin Descriptions (Continued)

| PIN NO. | SYMBOL             | I/O | DESCRIPTION                                                                                                                                                                                                                                                            |  |  |  |

|---------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 28      | вск                | I/O | Serial bit transfer clock for serial input data SIN or serial output data SOUT (64FS). Outputs in master mode (when Pin 26 is High). Inputs in slave mode (when Pin 26 is Low). Retrieves serial input data at; send serial output data at; send serial output data at |  |  |  |

| 29      | SIN                | I   | Serial data input of 2-channel sampling. The data format is 2's complement, and consists of 32-bit slot.                                                                                                                                                               |  |  |  |

| 30      | SOUT               | 0   | Serial data output of 2-channel per sampling. The data format is 2's comple-<br>ment, and consists of 32-bit slot.                                                                                                                                                     |  |  |  |

| 31      | DV <sub>SS</sub>   | _   | Digital GND                                                                                                                                                                                                                                                            |  |  |  |

| 32      | MASL               | I   | Selects whether 16-bit serial data is applied in the first 16-bits or the last 16-<br>bit of 32-bit slot in serial I/O. High = Frontward truncation; Low = Rearward truncation                                                                                         |  |  |  |

| 33      | MLSL               | I   | Selects whether 16-bit serial data is input/output at LSB first or MSB f<br>serial I/O. High = MSB first; Low = LSB first                                                                                                                                              |  |  |  |

| 34      | XSLO               | I   | Crystal oscillator selection. Three bits, XSL0 to 2. Selects the clock frequency to be input from XTLI (Pin 7).                                                                                                                                                        |  |  |  |

| 35      | XSL1               | I   | Crystal oscillator selection. Three bits, XSL0 to 2. Selects the clock frequency to be input from XTLI (Pin 7).                                                                                                                                                        |  |  |  |

| 36      | XSL2               | I   | Crystal oscillator selection. Three bits, XSL0 to 2. Selects the clock frequency to be input from XTLI (Pin 7).                                                                                                                                                        |  |  |  |

| 37      | DASLO              | I   | IC measurement. Normally, fixed at High.                                                                                                                                                                                                                               |  |  |  |

| 38      | DASL1              | I   | IC measurement. Normally fixed at Low.                                                                                                                                                                                                                                 |  |  |  |

| 39      | WO                 | I   | Window masked when High; window open when Low (forced synchroniza-<br>tion). Equipped with a pull-up resistor.                                                                                                                                                         |  |  |  |

| 40      | DV <sub>DD</sub>   | _   | Digital power supply                                                                                                                                                                                                                                                   |  |  |  |

| 41      | NC                 | _   |                                                                                                                                                                                                                                                                        |  |  |  |

| 42      | NC                 | _   |                                                                                                                                                                                                                                                                        |  |  |  |

| 43      | SUB                | _   | Connected to the substrate in the IC (having the same potential as power sup ply). Connect this pin to GND via capacitor on the external printed wiring board.                                                                                                         |  |  |  |

| 44      | AV <sub>DD</sub> 1 | —   | Analog power supply for channel-1 AD converter                                                                                                                                                                                                                         |  |  |  |

| 45      | AIN1               | I   | Analog input of channel-1 AD converter                                                                                                                                                                                                                                 |  |  |  |

| 46      | AV <sub>SS</sub> 1 | —   | Analog GND for channel-1 AD converter                                                                                                                                                                                                                                  |  |  |  |

| 47      | AV <sub>SS</sub> 3 | —   | Analog GND for channel-1 DA converter                                                                                                                                                                                                                                  |  |  |  |

| 48      | AOUT1 (+)          | 0   | Analog forward phase output of channel-1 DA converter                                                                                                                                                                                                                  |  |  |  |

#### Absolute Maximum Ratings T<sub>A</sub> = 25°C

| Supply Voltage (V <sub>DD</sub> )               | V <sub>SS</sub> -0.5V to 7.0V                |

|-------------------------------------------------|----------------------------------------------|

| Input Voltage (V1)VSS                           | $_{\rm S} = 0.5$ V to V <sub>DD</sub> + 0.5V |

| Output Voltage (V <sub>0</sub> )V <sub>SS</sub> | $S = 0.5V$ to $V_{DD} = 0.5V$                |

| Operating Temperature (Topr)                    | 20 <sup>0</sup> C to 75 <sup>0</sup> C       |

| Storage Temperature (Tstg                       |                                              |

#### **Recommended Operating Conditions**

|                                               | MIN                | ТҮР  | MAX                |

|-----------------------------------------------|--------------------|------|--------------------|

| Supply Voltage (Note 1) (V <sub>DD</sub> )    | 4.5V               | 5.0V | 5.5V               |

| Ambient Temperature (T <sub>A</sub> )         | -20 <sup>0</sup> C | _    | +75 <sup>0</sup> C |

| Sampling Frequency (Note 2) (F <sub>S</sub> ) | 7kHz               | _    | 33kHz              |

#### I/O Capacitance

|                                                   | MIN    | ТҮР | MAX   |

|---------------------------------------------------|--------|-----|-------|

| Input Pin (C <sub>IN</sub> )                      | . —    | —   | 9pF   |

| Output Pin (C <sub>OUT</sub> )                    |        |     | 11pF  |

| Bidirectional Pin (C <sub>I/O</sub> )             |        | —   | 11 pF |

| Measurement conditions: $V_{DD} = V_1 = 0V$ , f = | = 1MHz |     |       |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. The analog power supplies for AD converters (Pins 17 and 44) must be turned on simultaneously with or before other poser supplies. turning on these power supplies after any other power supply may cause the device to fall into latch-up condition. this precaution, however, does not apply when turning off the power supplies.

- 2. Although the device can operate with  $F_S$  frequencies such as  $F_S = 44.1$  kHz or 48kHz, its analog characteristics deteriorate to extent. When used at only these  $F_S$  frequencies, the CXD255Q is recommended that is pin-compatible with the CXD2570Q.

|                      |                                                          | TEST                                                                                             |                      | RT NUM  |                                     | UNITS                             | APPLICABLE<br>PINS                    |

|----------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|---------|-------------------------------------|-----------------------------------|---------------------------------------|

| PARAMETER            | SYMBOL                                                   | CONDITIONS                                                                                       | MIN                  | ТҮР     | MAX                                 |                                   |                                       |

| DC Characteristics   |                                                          | $AV_{DD}3 = AV_{DD}4 = XV_{DD} =$<br>/, T <sub>A</sub> = -20 <sup>o</sup> C to 75 <sup>o</sup> C | $DV_{DD} = 5.0V \pm$ | 10%, A' | V <sub>SS</sub> 1 = AV <sub>S</sub> | <sub>S</sub> 2 = AV <sub>SS</sub> | <sub>3</sub> 3 = AV <sub>SS</sub> 4 = |

| Input Voltage        | V <sub>IHC</sub>                                         |                                                                                                  | 0.7V <sub>DD</sub>   | _       | _                                   | V                                 | *1                                    |

|                      | V <sub>ILC</sub>                                         |                                                                                                  | Ò                    | Ò       | 0.3V <sub>DD</sub>                  | 1                                 |                                       |

|                      | V <sub>IN</sub>                                          | Analog Input                                                                                     | V <sub>SS</sub>      | —       | V <sub>DD</sub>                     | V                                 | *2                                    |

| Output Voltage       | V <sub>OH1</sub>                                         | I <sub>OH</sub> = -2mA                                                                           | V <sub>DD</sub> -0.5 | —       | V <sub>DD</sub>                     | V                                 | *3                                    |

|                      | V <sub>OL1</sub>                                         | I <sub>OL</sub> = 4mA                                                                            | 0                    | _       | 0.4                                 | 1                                 |                                       |

|                      | V <sub>OH2</sub>                                         | I <sub>OH</sub> = -4mA                                                                           | V <sub>DD</sub> -0.5 | —       | V <sub>DD</sub>                     | V                                 | *4                                    |

|                      | V <sub>OL2</sub>                                         | I <sub>OL</sub> = 4mA                                                                            | 0                    | —       | 0.4                                 | 1                                 |                                       |

|                      | V <sub>OH3</sub>                                         | I <sub>OH</sub> = -12mA                                                                          | V <sub>DD</sub> /2   | _       | V <sub>DD</sub>                     | V                                 | *5                                    |

|                      | V <sub>OL3</sub>                                         | I <sub>OL</sub> = 16mA                                                                           | 0                    | _       | V <sub>DD</sub> /2                  |                                   |                                       |

|                      | V <sub>OH4</sub>                                         | I <sub>OH</sub> = -2mA                                                                           | V <sub>DD</sub> -0.8 | —       | V <sub>DD</sub>                     | V                                 | *6                                    |

|                      | V <sub>OL4</sub>                                         | I <sub>OL</sub> = 4mA                                                                            | 0                    | _       | 0.4                                 | 1                                 |                                       |

| Input Leak Current 1 | I <sub>LI1</sub>                                         |                                                                                                  | -10                  | _       | 10                                  | μA                                | *7                                    |

| Input Leak Current 2 | I <sub>LI2</sub>                                         |                                                                                                  | -40                  | —       | 40                                  | μA                                | *8                                    |

| Input Leak Current 3 | I <sub>LI3</sub>                                         |                                                                                                  | -20                  | -50     | -12-                                | μA                                | *9                                    |

| Input Leak Current 4 | I <sub>LI4</sub>                                         |                                                                                                  | 20                   | 50      | 120                                 | μA                                | *10                                   |

| Output Leak Current  | I <sub>LZ</sub>                                          |                                                                                                  | -40                  | —       | 40                                  | μA                                | *11                                   |

| Feedback Resistance  | R <sub>FB</sub>                                          | $V_{IN} = V_{SS} \text{ or } V_{DD}$                                                             | 250K                 | 1M      | '2.5M                               | Ω                                 | *12                                   |

| Supply Current       | I <sub>DD</sub>                                          | (Note 3)                                                                                         | —                    | 43      | 60                                  | mA                                |                                       |

| AC Characteristics   | $AV_{DD}1 = AV_{DD}2 =$<br>$XV_{SS} = DV_{SS} = 0V_{SS}$ | $AV_{DD}3 = AV_{DD}4 = XV_{DD} =$<br>/, T <sub>A</sub> = -20 <sup>o</sup> C to 75 <sup>o</sup> C | $DV_{DD} = 5.0V \pm$ | 10%, A' | V <sub>SS</sub> 1 = AV <sub>S</sub> | <sub>S</sub> 2 = AV <sub>SS</sub> | <sub>3</sub> 3 = AV <sub>SS</sub> 4 = |

| SIN Setup Time       | tsus                                                     |                                                                                                  | 10                   | —       | —                                   | ns                                |                                       |

| SIN Hold Time        | ths                                                      |                                                                                                  | 15                   | —       | _                                   | ns                                |                                       |

| LRCK Setup Time      | tsul                                                     | Slave mode                                                                                       | 10                   | -       | —                                   | ns                                |                                       |

| LRCK Hold Time       | thl                                                      | Slave mode                                                                                       | 15                   | —       | —                                   | ns                                |                                       |

| LRCK Delay Time      | tdl                                                      | Master mode<br>CL = 130pF                                                                        | -40                  | -       | 30                                  | ns                                |                                       |

#### **Electrical Specifications**

| Electrical Specifications | (Continued) |

|---------------------------|-------------|

|---------------------------|-------------|

|                                 |        | TEST                                           | PART NUMBER<br>OR GRADE |     |     | APPLICABLE |      |

|---------------------------------|--------|------------------------------------------------|-------------------------|-----|-----|------------|------|

| PARAMETER                       | SYMBOL | CONDITIONS                                     | MIN                     | TYP | MAX | UNITS      | PINS |

| SOUT Delay Time                 | tds    | CL = 60pF                                      | 9                       | —   | 65  | ns         |      |

| SOUT Data Recovery Time         | tzd    |                                                | 7                       | —   | 42  | ns         |      |

| SOUT Data Erase Time            | tdz    |                                                | 6                       | —   | 40  | ns         |      |

| XTLI Pulse Width for Low Period | twl    | FS = 16kHz, 256Fs<br>(XSL0 = XSL1 = XSL2 = Low | 40                      | _   | 200 | ns         |      |

NOTES:

3. This includes current consumption at load resistance (RL =  $3.9\Omega$ ). Fs = 16kHz

\*1 All input pins except AIN1 and AIN2, and when bidirectional pins (BCK and LRCK) are input mode.

\*2 AIN1, AIN2

\*3 XCLK, XMCK2, SOUT

\*4 AOUT1 (+), AOUT1 (-), AOUT2 (+), AOUT2 (-), UCLK

\*5 XTLO

\*6 When bidirectional pins (BCK and LRCK) are output mode

\*7 All input pins except AIN1 and AIN2

\*8 When directional pins (BCK and LRCK) are input mode

\*9 MS, WO, CLR

\*10 TEST

\*11 SOUT, AOUT1 (+), AOUT1 (-), AOUT2 (+), AOUT2 (-), UCLK

\*12 Resistance between XTLO and XTLI

Analog Characteristics  $AV_{DD}1 = AV_{DD}2 = AV_{DD}3 = AV_{DD}4 = XV_{DD} = DV_{DD} = 5.0V \pm 10\%$ ,  $AV_{SS}1 = AV_{SS}2 = AV_{SS}3 = AV_{SS}4 = XV_{SS} = DV_{SS} = 0V$ ,  $T_A = 25^{\circ}C$

| ITEM                                                                                                                                                                                    | CONDITIONS                         | MIN.                | TYP.               | MAX.            | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|--------------------|-----------------|------|

| ADC + DAC Connection Overall Character<br>Input waveform = 1kHz sine wave, 1.4'<br>XTAI = 16.384MHz (= 1024Fs, Fs = 16<br>CLR = MS = WO = open (= 5V)<br>SOUT and SIN directly coupled. | /rms (= 0dB), $R_{IN} = 16k\Omega$ | e following condit  | ions unless otherw | vise specified. |      |

| S/N Ratio                                                                                                                                                                               | 8kHz LPF                           | 74                  | 80                 | —               | dB   |

| THD + N                                                                                                                                                                                 | 8kHz LPF                           | —                   | 0.015              | 0.03            | %    |

| Dynamic Range                                                                                                                                                                           | 1kHz, -60dB<br>8kHz LPF            | 74                  | 80                 | _               | dB   |

| Channel Separation                                                                                                                                                                      | 1kHz, 0dB                          | —                   | 97                 |                 | dB   |

| Gain Difference Between Channels                                                                                                                                                        |                                    | —                   | 0.1                | _               | dB   |

| Gain                                                                                                                                                                                    | RL = 3.9kW                         | -3                  | 0                  | +3              | dB   |

| Input Level                                                                                                                                                                             | R <sub>IN</sub> = 0Ω               | _                   | 0.1                | _               | Vrms |

|                                                                                                                                                                                         | R <sub>IN</sub> = 16Ω              | _                   | 1.4                | _               | Vrms |

| DC Offset (ADC Output)                                                                                                                                                                  |                                    | _                   | 030F               | _               | Hex  |

| ADC Input Impedance                                                                                                                                                                     |                                    | —                   | 1.2                |                 | kΩ   |

| DAC characteristics in a single unit. Mea:<br>Input data = 1kHz sine wave, full scale<br>XTAI = 16.384MHz (= 1024Fs, Fs = 16<br>CLR = WO = open (= 5V), MS = GND                        | (= 0dB)                            | conditions unless c | therwise specified | l.              |      |

| S/N Ratio                                                                                                                                                                               | 8kHz LPF                           | 84                  | 90                 | _               | dB   |

| THD + N                                                                                                                                                                                 | 8kHz LPF, -3dB                     |                     | 0.009              | 0.03            | %    |

| Dynamic Range                                                                                                                                                                           | 1kHz, -60dB<br>8kHz LPF            | 82                  | 88                 |                 | dB   |

Analog Characteristics  $AV_{DD}1 = AV_{DD}2 = AV_{DD}3 = AV_{DD}4 = XV_{DD} = DV_{DD} = 5.0V \pm 10\%$ ,  $AV_{SS}1 = AV_{SS}2 = AV_{SS}3 = AV_{SS}4 = XV_{SS} = DV_{SS} = 0V$ ,  $T_A = 25^{\circ}C$  (Continued)

| ITEM                             | CONDITIONS     | MIN. | TYP. | MAX. | UNIT |

|----------------------------------|----------------|------|------|------|------|

| Channel Separation               | 1kHz, 0dB      | —    | 100  | _    | dB   |

| Gain Difference Between Channels |                | —    | 0.05 | _    | dB   |

| Output Level                     | $R_L = 3.9 kW$ | 1.80 | 1.93 | 2.10 | Vrms |

# **Description of Functions**

1. Serial data interface

[Related pins] LRCK, BCK, SOUT, SIN, MASL, MLSL

The serial data format is common for both SIN (DA converter input) and SOUT (AD converter output), consisting of two channels per sampling serial data represented by 2's complement. Each channel is divided into 32-bit slots, of which 16 bits are handled as data.

MASL is used to select whether the 16 bits of valid data is placed in the first or the last half of the 32-bit slots.

Similarly, MLSL is used to select whether the serial data is arranged at MSB first of LSB first.

| MASL |                      | MLSL |           |

|------|----------------------|------|-----------|

| High | Frontward truncation | High | MSB first |

| Low  | Rearward truncation  | Low  | LSB first |

2. Master mode/slave mode

[Related pins] MS, LRCK, BCK

When using the CXD2570Q in multiple units or in a pair with DA converter such as the CXD2558M, one of these CXD2570Qs should be in the master mode to serve as the source of clocks LRCK and BCK.

The other ICs including CXD2570Qs are used in the slave mode, with their clocks LRCK and BCK supplied by the master CXD2570Q.

| MS   | MODE        | LRCK AND BCK I/O |  |

|------|-------------|------------------|--|

| High | Master mode | Output           |  |

| Low  | Slave mode  | Input            |  |

3. Crystal oscillator frequency selection (FS = 16kHz to 48kHz)

[Related pins] XTLI, XTLO, XSL0, XSL1, XSL2, UCLK, XCLK

By setting a combination of XSL0 and XSL1, with XSL2 fixed low, the frequency of the external crystal oscillator connected to XTLI and XTLO can be selected. In this case, XCLK outputs a clock whose frequency is always 256 times Fs, and UCLK outputs a clock that is half the crystal oscillator frequency.

When supplying the master clock from some other external source, not a crystal oscillator, use XTLI for this clock input and leave XTLO open.

| XSL2 | XSL1 | XSL0 | CRYSTAL<br>OSCILLATOR<br>FREQUENCY | XCLK  | UCLK  |

|------|------|------|------------------------------------|-------|-------|

| L    | L    | L    | 256Fs                              | 256Fs | 128Fs |

| L    | L    | н    | 512Fs                              | 256Fs | 256Fs |

| L    | н    | L    | 768Fs                              | 256Fs | 384Fs |

| L    | Н    | Н    | 1024Fs                             | 256Fs | 512Fs |

\*The CXD2555Q, which has the same pin configuration with this IC is recommended when using only Fs = 32kHz to 48kHz.

4. Crystal oscillator frequency selection (FS = 8kHz to 16kHz)

[Related pins] XTLI, XTLO, XSL0, XSL1, XSL2, UCLK, XCLK

With XSL2 fixed High, the device can be operated with low-Fs frequencies. In this case, the frequency of the crystal oscillator can be selected by setting a combination of XSL0 and XSL1 accordingly.

| XSL2 | XSL1 | XSL0 | CRYSTAL<br>OSCILLATOR<br>FREQUENCY* | XCLK  | UCLK  |

|------|------|------|-------------------------------------|-------|-------|

| Н    | L    | L    | 512Fs                               | 512Fs | 256Fs |

| н    | L    | н    | —                                   | —     | —     |

| н    | н    | L    | 1024Fs                              | 512Fs | 512Fs |

| Н    | Н    | Н    | _                                   | —     | —     |

5. A/D converter input level

Any desired input level  $V_{IN}$  (m . 0.1Vrms) can be selected by adjusting  ${\rm R}_{IN}$  to generate the full-scale output of the AD converter.

$V_{\rm IN}$  generation of full-scale output varies with the products, and calculate the  $V_{\rm IN}$  maximum level (approximately -3dB below the full-scale) using the following equation to input the signal.

(1) Fs = 16kHz to 48kHz (XSL2 = Low)

$$R_{IN} = 1230 \cdot V_{IN} [Vrms] -1200 (\Omega)$$

(2) Fs = 8 to 16kHz (XSL2 = High)

$R_{IN} = 26600 \cdot V_{IN} [Vrms] -1200 (\Omega)$

#### 6. D/A converter output level

To change the D/A converter output level, adjust R15, R17, R30 and R32 in Application Circuit on page.

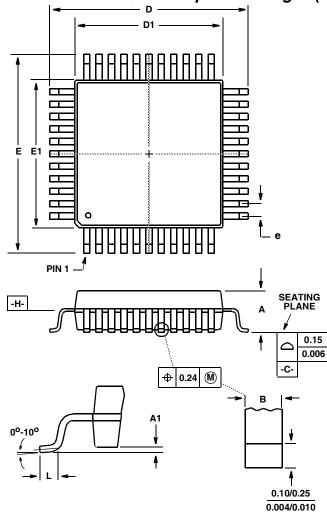

# Metric Plastic Quad Flatpack Packages (MQFP)

#### Q48.12x12-S

48 LEAD METRIC PLASTIC QUAD FLATPACK PACKAGE

|        | INCHES    |       | MILLIMETERS |       |       |

|--------|-----------|-------|-------------|-------|-------|

| SYMBOL | MIN       | MAX   | MIN         | MAX   | NOTES |

| A      | 0.081     | 0.100 | 2.05        | 2.55  | -     |

| A1     | 0.000     | 0.011 | 0.00        | 0.30  | -     |

| В      | 0.008     | 0.017 | 0.20        | 0.45  | 5     |

| D      | 0.587     | 0.618 | 14.90       | 15.70 | 2     |

| D1     | 0.469     | 0.488 | 11.90       | 12.40 | 3, 4  |

| E      | 0.587     | 0.618 | 14.90       | 15.70 | 2     |

| E1     | 0.469     | 0.488 | 11.90       | 12.40 | 3, 4  |

| L      | 0.028     | 0.043 | 0.70        | 1.10  | -     |

| Ν      | 48        |       | 48          |       | 6     |

| е      | 0.032 BSC |       | 0.80        | BSC   | -     |

NOTES:

- Rev. 0 2/96

- 1. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 2. Dimensions D and E to be determined at seating plane -C-

- 3. Dimensions D1 and E1 to be determined at datum plane -H-

- 4. Dimensions D1 and E1 do not include mold protrusion.

- 5. Dimension B does not include dambar protrusion.

- 6. "N" is the number of terminal positions.